Пересказ статьи Lenovo Press, перевод SMB-Solution.

Раньше с памятью было всё просто: чем больше поставил, тем лучше. Сейчас всё стало сложнее, появились многопроцессорные системы, в процессорах есть контроллеры памяти, в каждом из них имеются каналы памяти. Появился такой термин как балансировка памяти.

Балансировка памяти при конфигурировании сервера важна для достижения максимума пропускной способности памяти и общей производительности сервера. Процессоры Intel Xeon имеют 4 или 8 каналов памяти и позволяют установить до трех модулей DIMM на канал, поэтому важно понять, что считается сбалансированной конфигурацией, а что нет.

В этой статье мы представляем три принципа балансировки памяти, которые помогут вам выбрать оптимальную конфигурацию памяти. Сбалансированные и несбалансированные конфигурации памяти представлены вместе с их измеренной относительной шириной полосы пропускания, чтобы показать эффект, который привносит несбалансированнсть памяти. Также предлагаются предложения по созданию сбалансированных конфигураций памяти.

Введение

Подсистема памяти является ключевым компонентом архитектуры серверов на базе процессоров Intel Xeon, которая может повлиять на общую производительность сервера. При правильной настройке подсистема может обеспечить чрезвычайно высокую пропускную способность и низкую задержку доступа к памяти.

Однако, если подсистема памяти неправильно настроена, пропускная способность памяти, доступной серверу, может стать ограниченной, а общая производительность сервера может упасть.

В этом кратком руководстве объясняется концепция сбалансированных конфигураций, которые обеспечивают максимально возможную пропускную способность памяти в архитектуре Intel Xeon. Примеры сбалансированных и несбалансированных конфигураций иллюстрируют их влияние на производительность подсистемы памяти.

Эта статья применима к серверам на базе процессоров Intel Xeon E5 v4 и будущих процессоров E7 v4, а также к семействам процессоров предыдущего поколения Xeon E5 v3 и E7 v3.

Чередование памяти

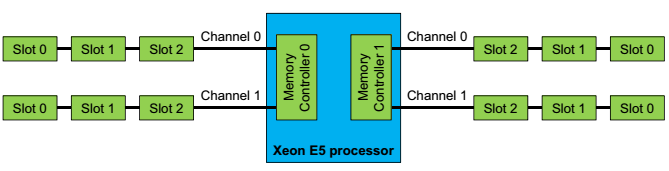

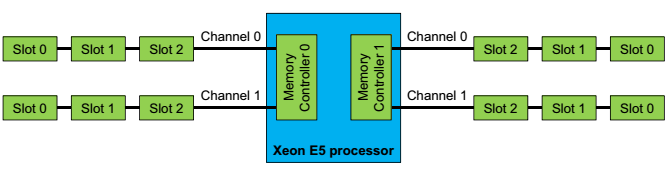

Доступ к информации, хранящейся в памяти DIMM, управляется контроллерами памяти в процессоре Intel Xeon. В зависимости от конкретного процессора, он содержит один или два контроллера памяти. Каждый контроллер памяти подключен к каналам памяти, которые, в свою очередь, подключены к физическим разъемам, в которые устанавливаются модули памяти DIMM.

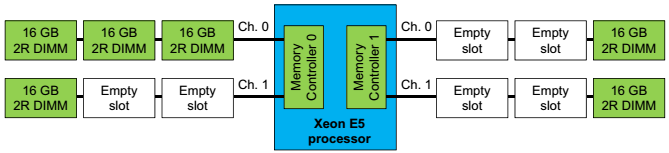

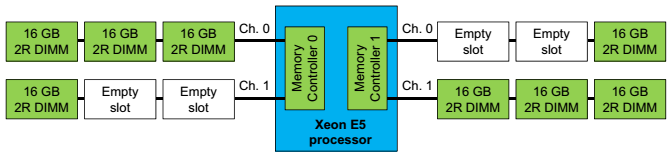

Рисунок 1 показывает, как контроллеры памяти процессора Intel E5 подключены к слотам (разъёмам) DIMM.

Процессор Xeon оптимизирует обращения к памяти путем создания наборов чередования между контроллерами памяти и/или каналами памяти. Например, если идентичные модули DIMM установлены на обоих каналах, контроллера памяти, он создает двухполосное чередование между этими двумя модулями DIMM. На рисунке 2 показаны два таких набора чередования.

| Двухполосное чередование |

Двухполосное чередование |

|

|

Чередование позволяет увеличить пропускную способность памяти за счет одновременной посылки запросов в оба канала памяти, а не последовательного формирования запросов в одном из каналов.

Если различные по объему модули памяти устанавливаются в один канал или если на каналах памяти установлено различное количество идентичных по емкости модулей DIMM, контроллер памяти должен создавать множество наборов чередования. Управление множеством наборов чередования создает дополнительные накладные расходы для контроллера, что может уменьшить пропускную способность системы памяти.

На рисунке 2 показано двухполосное чередование памяти на процессоре Intel E5 в результате установки идентичных модулей памяти DIMM на каждом канале памяти. Двухполосное чередование может быть расширено чередованием между контроллерами памяти. Последовательные адреса будут перемежаться между контроллерами памяти, когда каждый четвертый адрес поступает на каждый канал памяти.

В канале памяти может быть организован второй уровень чередования, называемый чередованием ранков памяти. Ранк памяти — это блок данных, созданный из микросхем памяти в модуле DIMM. Ширина ранка памяти обычно составляет 64 бита. Если поддерживается ECC, добавляются дополнительные 8 бит до общей ширины в 72 бит. Модуль DIMM может содержать несколько ранков памяти, например, один, два и четыре ранка на модуль DIMM. Чередование ранков памяти оптимально, когда все модули DIMM на канале памяти имеют одинаковое количество ранков памяти. Например, каждый модуль DIMM на канале памяти является 2-ранковым DIMM.

При установке модулей памяти на свой сервер следуйте последовательности установки DIMM, описанной для вашего конкретного сервера. Конфигурации, показанные в этом документе, не всегда соответствуют рекомендованным последовательностям для серверов, на которых они были реализованы и измерены, поскольку ряд этих конфигураций был собран только для демонстрационных целей.

Сбалансированные конфигурации памяти

Сбалансированные конфигурации обеспечивают оптимальное чередование по всем подключенным каналам памяти, то обеспечивает максимальную пропускную способность. Полоса пропускания может быть оптимизирована, если оба контроллера памяти в одном физическом процессоре имеют идентичную конфигурацию. Производительность памяти системного уровня может быть дополнительно оптимизирована, если каждый физический процессор имеет один и тот же объем физической памяти.

В результате основные принципы сбалансированной подсистемы памяти заключаются в следующем:

- Все заполненные каналы памяти должны иметь одинаковую общую емкость памяти и одинаковое общее количество ранков.

- Все контроллеры памяти в процессорном сокете должны иметь одинаковую конфигурацию модулей DIMM.

- Все сокеты процессора на одном физическом сервере должны иметь одинаковую конфигурацию модулей DIMM.

Примечание. Мы ссылаемся на вышеуказанные три пункта на протяжении всей этой статьи как на правила балансировки 1, 2 и 3.

Описание теста STREAM

STREAM Triad — простой, синтетический эталонный тест, предназначенный для измерения устойчивой пропускной способности памяти. Его цель — измерить лучшую доступную пропускную способность памяти. STREAM Triad будет использоваться для измерения постоянной пропускной способности различных конфигураций, чтобы увидеть влияние баланса на пропускную способность памяти.

http://www.cs.virginia.edu/stream/

Топология памяти

В этой статье мы тестируем сервер с процессором E5-2600 v3 с двумя контроллерами памяти, однако результаты одинаково применимы к серверам с процессорами E5-2600 v4.

Процессоры Xeon E5 нижнего диапазона: процессоры Intel Xeon E5 v3 с менее чем 10 ядрами и процессоры E5 v4 с менее чем 12 ядрами имеют только один контроллер памяти. Все четыре канала памяти подключены к одному контроллеру. В результате, правило балансировки 2 не применимо для процессоров с одним контроллером памяти.

В иллюстрациях различные топологии памяти для процессора с двумя контроллерами будут обозначаться как A:B:C:D, где каждая буква указывает количество модулей DIMM, установленных на каждом канале памяти.

- ► A - канал памяти 0 на контроллере памяти 0

- ► B - канал памяти 1 контроллера памяти 0

- ► C - канал памяти 0 на контроллере памяти 1

- ► D - канал памяти 1 контроллера памяти 1

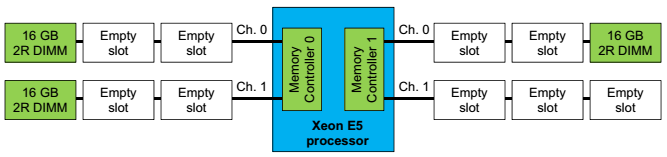

Это обозначение показано на рисунке 3.

Например, конфигурация памяти 3: 2: 1: 0 имеет:

- ► 3 модуля DIMM на канале памяти 0 на контроллере памяти 0

- ► 2 модуля DIMM на канале памяти 1 на контроллере памяти 0

- ► 1 модуль DIMM на канале памяти 0 на контроллере памяти 1

- ► 0 модулей DIMM на канале памяти 1 на контроллере памяти 1

Применение правил балансировки памяти — процессоры E5

Начнем с предположения о том, что правило балансировки памяти 3, описанное в разделе «Сбалансированные конфигурации памяти» на стр. 4, соблюдается и все процессоры на одном физическом сервере имеют одинаковую конфигурацию модулей DIMM.

Конфигурация из 4 модулей DIMM — сбалансированная

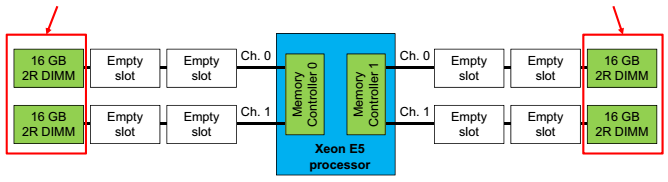

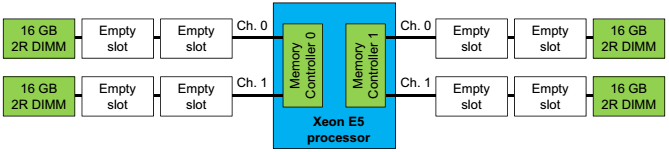

Поэтому нам нужно посмотреть только один процессорный сокет для каждой конфигурации памяти. Мы начнем с одного модуля DIMM в каждом канале памяти, который даст конфигурацию памяти 1:1:1:1, показанную на рисунке 4.

(относительная полоса пропускания STREAM = 100)

Это сбалансированная конфигурация памяти, так как она соответствует правилу балансировки 1 с двух-ранковыми модулями 16 ГБ на всех каналах памяти. Она также соответствует правилу 2, поскольку оба контроллера памяти имеют одинаковую конфигурацию модулей DIMM.

Чередование может выполняться как между контроллерами памяти, так и по обеим парам каналов памяти. Конфигурация 1:1:1:1 обеспечивает максимальную пропускную способность памяти с относительной оценкой STREAM Triad 100.

Конфигурация из 5 модулей DIMM — несбалансированная

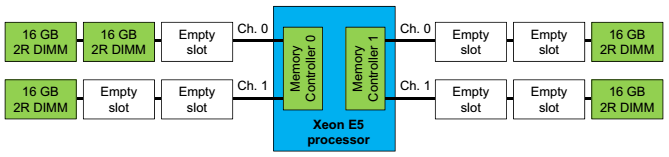

Добавляем один модуль памяти, чтобы посмотреть, как это повлияет на пропускную способность системы. Конфигурация 2:1:1:1 показана на рисунке 5.

(относительная полоса пропускания STREAM = 26)

Это не сбалансированная конфигурация памяти, так как она ломает сразу 2 правила балансировки памяти: 1 — различная ёмкость и число ранков памяти на разных каналах; 2 — различные конфигурациями DIMM на контроллерах памяти.

На контроллере 1 создается 2-полосный набор чередования. Контроллер 0 должен создать два отдельных набора чередования для трех модулей DIMM на двух его каналах памяти:

- ► 2-полосный набор чередования создается с использованием одного модуля DIMM из каждого канала памяти.

- ► 1-полосный набор чередования создается с использованием оставшегося DIMM на контроллере 0 Channel 0.

Чередование по контроллерам памяти не выполняется для этой конфигурации из-за несбалансированной памяти между ними. Невозможность чередования между контроллерами памяти в сочетании со служебными данными чередования на канале памяти 0 уменьшает пропускную способность памяти конфигурации памяти 2:1:1:1 до 26% относительно конфигурации памяти 1:1:1:1.

Конфигурация из 6 модулей DIMM – 3 не сбалансированы, 1 сбалансирован

Существует множество способов заполнения шести модулей DIMM в двенадцати слотах. Мы рассмотрим четыре разных способа, чтобы увидеть их влияние на пропускную способность памяти.

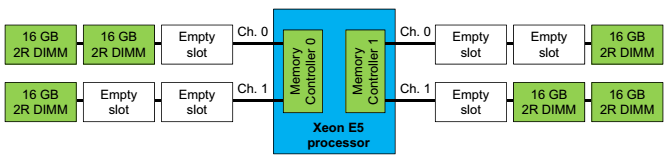

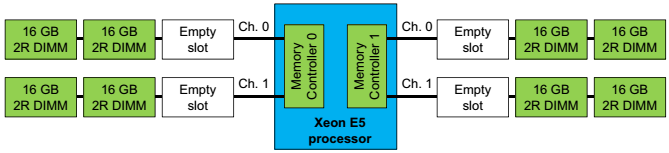

Первый — это конфигурация памяти 2:1:1:2, показанная на рисунке 6.

(относительная полоса пропускания STREAM = 52)

Это несбалансированная конфигурация памяти, так как она не соответствует правилу балансировки памяти 1: два канала памяти имеют по 32 ГБ памяти и в сумме четыре ранка, в то время как другие два имеют только 16 ГБ памяти и два ранка. Правило балансировки 2 выполняется, так как оба контроллера памяти имеют одинаковую конфигурацию модулей памяти DIMM, что позволяет осуществлять чередование по контроллерам памяти.

Каждый контроллер памяти должен создать два отдельных набора чередования для трех модулей DIMM на своих двух каналах памяти, как описано выше для контроллера памяти 0 в конфигурации памяти 2:1:1:1. Правило балансировки 2 соблюдается, так как контроллеры имеют симметричную конфигурацию DIMM. Несмотря на это, накладные расходы на чередование нескольких наборов на каналах уменьшают относительную пропускную способность памяти в конфигурации 2:1:1:2 до 52.

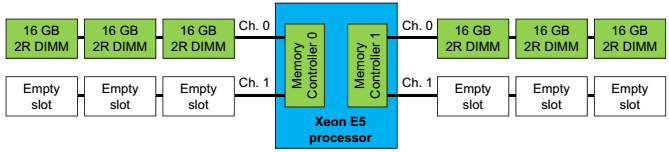

Второй способ установки 6 модулей DIMM — это конфигурация памяти 3: 1: 1: 1, показанная на рисунке 7.

(относительная полоса пропускания STREAM = 20)

Эта конфигурация несимметричной памяти не соответствует правилу балансировки памяти 1, так как один канал имеет больше объема памяти и ранков, чем другие. Он также не соответствует правилу 2, поскольку контроллеры памяти имеют различные конфигурации DIMM.

Чередование не может выполняться между контроллерами памяти. Контроллер 1 может чередовать свои каналы памяти, поскольку они соответствуют сбалансированной схеме памяти 1. Контроллер памяти 0 должен будет создать одно двух-полосное чередование по его каналам памяти и два набора 1-полосного чередования для двух модулей DIMM на его канале памяти 0.

Так как большая часть памяти этой конфигурации находится на контроллере памяти 0, накладные расходы чередования оказывают в такой конфигурации сильное негативное влияние. Результатом является относительная ширина полосы пропускания памяти 20.

Один из путей выполнения правила балансировки памяти 2 с шестью модулями DIMM — конфигурация памяти 3:0:3:0, показанная на рисунке 8.

(относительная полоса пропускания STREAM = 39)

Эта конфигурация памяти соответствует правилу балансировки памяти 1 и представляет собой сбалансированную конфигурацию. Тем не менее, все каналы памяти должны быть загружены для достижения максимальной пропускной способности памяти, а в конфигурации 3:0:3:0 задействованы только 2 из 4 каналов.

Чередование осуществляется между контроллерами памяти. Помимо этого, каждый контроллер памяти будет создавать три одно-полосных набора чередования на канале памяти 0.

Несмотря на то, что правило балансировки 2 выполняется, эта конфигурация имеет относительную пропускную способность памяти 39 — в основном, из-за не задействованного канала памяти 1 обоих контроллерах.

Примечание переводчика. В процессорах Xeon E5 v3 и v4 установка второго и третьего модуля DIMM на канал приводит к снижению на ступень скорости работы контроллера с модулями. Так, если на канал установлен один модуль, он может работать на частоте 2400 MHz. Установка второго модуля на тот же канал приводит к снижению частоты до, 2133 MHz. Третьего — до 1866 MHz. Это связано с нагрузкой на линии шины. Так что, несмотря на оптимизацию производительности, полученную за счет чередования, схема 3:0:3:0 не может считаться оптимальной в целом из-за снижения частоты шины.

Частота в конфигурациях 1 DIMM / канал (1DPC), 2 DIMM / канал (2DPC), 3 DIMM / канал (3DPC).

| Частота модуля DIMM | RDIMM | LRDIMM | ||||

| 1DPC | 2DPC | 3DPC | 1DPC | 2DPC | 3DPC | |

| DDR4-2400 | 2400 | 2133 | 1866 | 2400 | 2133 | 1866 |

| DDR4-2133 | 2133 | 2133 | 1866 | 2133 | 2133 | 1866 |

| DDR4-1866 | 1866 | 1866 | 1866 | 1866 | 1866 | 1866 |

Последний рассматриваемый способ организовать шесть модулей DIMM состоит в том, чтобы разместить их все на один контроллер памяти в схему 3: 3: 0: 0, как показано на рисунке 9.

(относительная полоса пропускания STREAM = 38)

Эта конфигурация памяти не соответствует правилу балансировки памяти 1 так же, как конфигурация памяти 3:0:3:0. Она также не соответствует правилу 2, так как вся память находится на одном контроллере памяти. Наличие одного не задействованного контроллера памяти полностью исключает его вклад в пропускную способность.

Чередование может происходить между каналами на контроллере памяти 0. Несмотря на это, конфигурация памяти 3:3:0:0 имеет относительную пропускную способность памяти лишь 38.

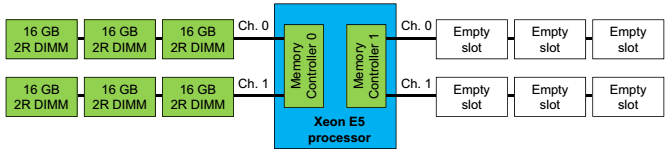

Конфигурация из 8 модулей DIMM – сбалансированная

Используя 8 модулей DIMM просто создать сбалансированную конфигурацию 2:2:2:2, как показано на рисунке 10.

(относительная полоса пропускания STREAM = 100)

Эта конфигурация памяти соответствует правилу балансировки памяти 1 с использованием всех каналов, заполненных одинаково, а также правилу 2, поскольку каждый контроллер памяти имеет одинаковую конфигурацию DIMM.

Эта конфигурация памяти может использовать чередование как между контроллерами памяти, так и между каналами памяти. Конфигурация 2:2:2:2 обеспечивает максимальную относительную пропускную способность памяти 100.

Конфигурация из 8 модулей DIMM – несбалансированная

Те же 8 модулей памяти могут быть размещены в несбалансированной конфигурации 3:1:1:3, как показано на рисунке 11.

(относительная полоса пропускания STREAM = 53)

Эта конфигурация не соответствует правилу балансировки памяти 1, так как половина каналов памяти имеет 48 ГБ памяти и 6 ранков, тогда как другие имеют только 16 ГБ памяти и 2 ранка.

Эта конфигурация памяти может чередоваться по контроллерам памяти, но не эффективна по каналам памяти. Каждый контроллер памяти будет иметь один двух-полосный набор чередования и два набора одно-полосного чередования. Такое сочетание снижает относительную пропускную способность памяти до 53.

Конфигурация из 3 модулей DIMM – несбалансированная

Еще одна конфигурация памяти, которую необходимо рассмотреть, состоит только из трех модулей памяти DIMM в конфигурации 1:1:1:0, показанной на рисунке 12.

(относительная полоса пропускания STREAM = 60)

Эта конфигурация несимметричной памяти не соответствует правилу балансировки памяти 1 с одним незадействованным каналом памяти и правилу 2 — два модуля DIMM на одном контроллере памяти и только один на другом.

Эта конфигурация памяти не может быть эффективно перемежена ни по контроллерам памяти, ни по каналам памяти контроллера памяти 1. Она может чередоваться только по каналам памяти контроллера памяти 0.

Она также теряет в производительности из-за отсутствием какого-либо вклада в пропускную способность памяти канала памяти 1 контроллера памяти 1, поскольку он не используется. Результатом является относительная ширина полосы пропускания памяти 60.

Сводная таблица производительности для процессоров Intel Xeon E5 v3, v4

| DIMM | Конфи- гурация |

Кол-во наборов чередования Кратность чередования, схема объединения |

Произво- дительность |

Сбалансированная/ несбалансированная |

| 3 | 1:1:1:0 | 1 2x MC0CH0D0:MC0CH1D0 |

60 | несбалансированная |

| 4 | 1:1:1:1 | 1 4x MC0CH0D0:MC0CH1D0:MC1CH0D0:MC1CH1D0 |

100 | сбалансированная |

| 5 | 2:1:1:1 | 3 2x MC1CH0D0:MC1CH1D0 2x MC0CH0D0:MC0CH1D0 1x MC0CH0D1 |

26 | несбалансированная |

| 6 | 2: 1: 1: 2 | 2 4x MC0CH0D0:MC0CH1D0:MC1CH0D0:MC1CH1D0 2x MC0CH0D1:MC1CH1D1 |

52 | несбалансированная |

| 6 | 3:1:1:1 | 4 2x MC0CH0D0:MC0CH1D0 1x MC0CH0D1 1x MC0CH0D2 2x MC1CH0D0:MC1CH1D0 |

20 | несбалансированная |

| 6 | 3:0:3:0 | 7 2x MC0CH0:MC1CH0 1x MC0CH0D0 1x MC0CH0D1 1x MC0CH0D2 1x MC1CH0D0 1x MC1CH0D1 1x MC1CH0D2 |

39 | несбалансированная |

| 6 | 3:3:0:0 | 1 2x MC0CH0:MC0CH1 |

38 | несбалансированная |

| 8 | 2:2:2:2 | 1 4x MC0CH0:MC0CH1:MC1CH0:MC1CH1 |

100 | сбалансированная |

| 8 | 3:1:1:3 | 3 4x MC0CH0D0:MC0CH1D0:MC1CH0D0:MC1CH1D0 2x MC0CH0D1:MC1CH1D1 2x MC0CH0D2:MC1CH1D2 |

53 | несбалансированная |

Применение принципов балансировки памяти для процессоров E7

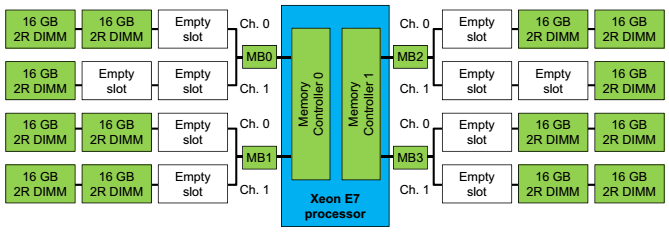

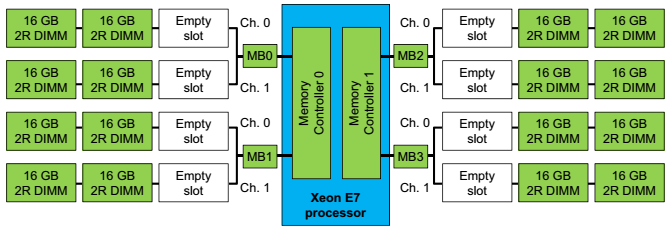

Процессор Intel Xeon E7 использует немного другую архитектуру памяти, чтобы обеспечить поддержку большего количества модулей DIMM.

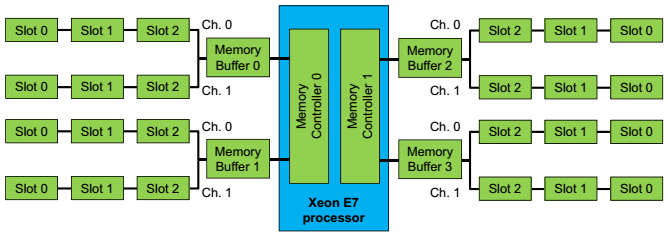

Каждый процессор Intel Xeon E7 имеет два встроенных контроллера памяти, и каждый контроллер памяти имеет две линии связи Scalable Memory Interconnect generation 2 (SMI2), которыми он подключается к двум масштабируемым буферам памяти. Каждый буфер памяти имеет два канала памяти, и каждый канал поддерживает три модуля DIMM — в общей сложности 24 модуля DIMM на процессор. Использование буферов памяти удваивает количество каналов памяти и модулей DIMM, поддерживаемых каждым процессором.

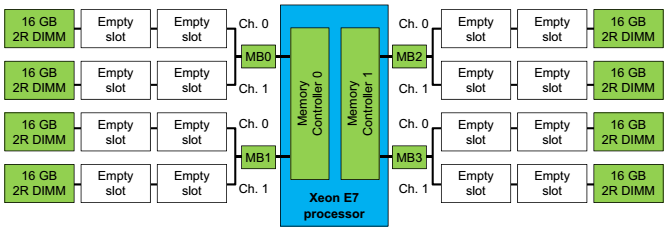

Архитектура памяти процессора E7 показана на рисунке 13.

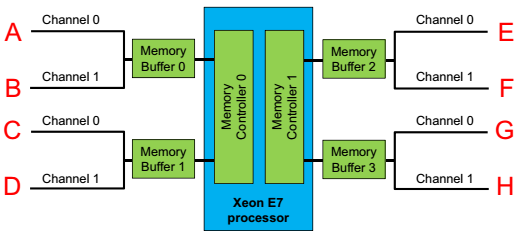

Конфигурации памяти будут обозначаться как A:B:C:D:E:F:G:H, где каждая буква указывает количество модулей DIMM, заполненных на каждом канале памяти.

- ► A относится к каналу памяти 0 в буфере памяти 0 на контроллере памяти 0

- ► B относится к каналу памяти 1 в буфере памяти 0 на контроллере памяти 0

- ► C относится к каналу памяти 0 в буфере памяти 1 контроллера памяти 0

- ► D относится к каналу памяти 1 в буфере памяти 1 контроллера памяти 0

- ► E относится к каналу памяти 0 в буфере памяти 2 контроллера памяти 1

- ► F относится к каналу памяти 1 в буфере памяти 2 контроллера памяти 1

- ► G относится к каналу памяти 0 в буфере памяти 3 на контроллере памяти 1

- ► H относится к каналу памяти 1 буфера памяти 3 контроллера памяти 1

Это обозначение показано на рисунке 14.

Буферы памяти обеспечивают еще один уровень, по которому может происходить чередование. Правило балансировки памяти 2 теперь одинаково применимо как к буферам памяти, как и к контроллерам памяти, поскольку все буферы памяти в процессорном сокете должны иметь одинаковую конфигурацию модулей DIMM, чтобы обеспечить эффективное чередование по ним.

Конфигурация из 8 модулей памяти — сбалансированная

Первая конфигурация памяти, которую рассматриваем, представляет собой сбалансированную конфигурацию памяти 1:1:1:1:1:1:1 с одним модулем DIMM на каждом канале памяти, как показано на рисунке 15. Эта конфигурация памяти соответствует всем правилам сбалансированной памяти и может эффективно чередоваться по контроллерам памяти, буферам памяти и каналам памяти. Она обеспечивает максимальную относительную пропускную способность памяти 100.

(относительная полоса пропускания STREAM = 100)

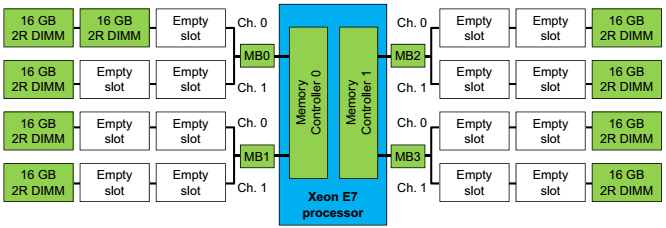

Конфигурация из 9 модулей памяти — несбалансированная

Добавим один модуль DIMM, чтобы получить несбалансированную конфигурацию памяти 2:1:1:1:1:1:1:1, как показано на рисунке 16.

(относительная полоса пропускания STREAM = 16)

Эта конфигурация не соответствует правилу балансировки памяти 1, т.к. имеет один канал памяти, имеющим в два раза больше памяти по объему и ранкам, чем все остальные. Он также не соответствует правилу балансировки 2, поскольку имеет различные конфигурации памяти на контроллерах, но он сбалансирован по буферам памяти на контроллере памяти 1.

Эффективное перемежение происходит между буфером памяти 2 и буфером памяти 3, поскольку оба они имеют одинаковые конфигурации подключенных модулей DIMM.

Трудно создавать чередование с нечетным количеством модулей DIMM. Результатом является очень низкая относительная пропускная способность памяти 16.

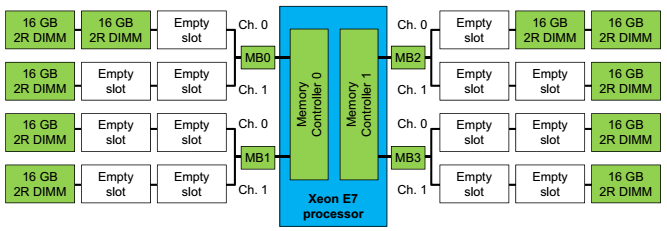

Конфигурация из 10 модулей памяти — несбалансированная

Добавим еще один модуль DIMM, чтобы получить несбалансированную конфигурацию памяти 2:1:1:1:2:1:1:1, как показано на рисунке 17.

(относительная полоса пропускания STREAM = 48)

Эта конфигурация соответствует правилу балансировки памяти 2 — оба контроллера памяти имеют одинаковые конфигурации DIMM, что позволяет чередовать модули памяти. Сбалансированная схема памяти не соблюдена для буферов памяти. Правило балансировки памяти 1 также не соблюдается, так как два канала памяти из восьми имеют удвоенную емкость памяти и количество ранков. Буферы памяти 1 и 3 выполняют правило балансировки 1, что позволяет осуществлять эффективное перемежение по каналам памяти. Результатом является относительная ширина полосы памяти 48.

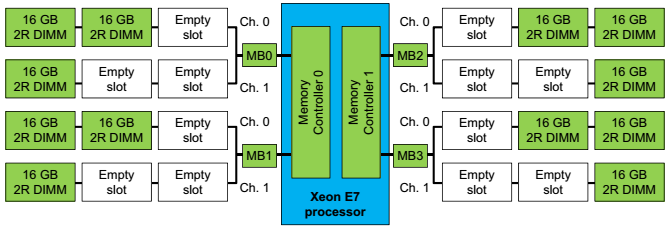

Конфигурация из 12 модулей памяти — несбалансированная

Добавляем еще два модуля DIMM, получаем схему 2:1:2:1:2:1:2:1, показанную на рисунке 18.

(относительная полоса пропускания STREAM = 64)

Для каждого контроллера памяти и всех буферов памяти с соответствующими конфигурациями DIMM соблюдаются правило балансировки памяти 2. Это позволяет использовать чередование между всеми ними. К сожалению, правило балансировки 1 памяти не соблюдается, так как половина каналов памяти имеет удвоенную емкость памяти и количество ранков. Результатом является менее эффективное перемежение по каналам каждого буфера и относительная ширина полосы памяти 64.

Конфигурация из 14 модулей памяти — несбалансированная

Используем 14 модулей DIMM, получаем схему 2:1:2:2:2:1:2:2, показанную на рисунке 19.

(относительная полоса пропускания STREAM = 33)

Эта конфигурация соответствует правилу балансировки памяти 2 — оба контроллера памяти имеют одинаковые конфигурации DIMM. Это позволяет эффективно чередовать между контроллерами памяти. Буферы памяти не соответствуют правилу балансировки 2, так как часть из них имеет три модуля DIMM, а часть — четыре. Правило балансировки 1 не соблюдается, поскольку не все каналы памяти имеют одинаковую емкость памяти и число ранков. Пары буферов памяти имеют одинаковые конфигурации DIMM: буферы памяти 0 и 2 и буферы памяти 1 и 3. Между этими парами буфера памяти можно эффективно осуществлять чередование. Результатом является относительная ширина полосы памяти 33.

Конфигурация из 16 модулей памяти — сбалансированная

Используем 16 модулей DIMM, получаем сбалансированную схему 2:2:2:2:2:2:2:2, показанную на рисунке 20.

(относительная полоса пропускания STREAM = 100)

Схема соответствует правилу балансировки памяти 1, поскольку все каналы памяти имеют одинаковую емкость памяти и количество ранков. Она также соответствует правилу балансировки 2, — оба контроллера памяти и все буферы памяти имеют одинаковые конфигурации DIMM. Это позволяет эффективно использовать чередование на всех уровнях и обеспечивает относительную пропускную способность памяти 100.

Сводная таблица производительности для процессоров Intel Xeon E7 v3

| DIMM | Конфигурация | Производительность | Сбалансированная/ несбалансированная |

| 8 | 1:1:1:1:1:1:1:1 | 100 | сбалансированная |

| 9 | 2:1:1:1:1:1:1:1 | 16 | несбалансированная |

| 10 | 2:1:1:1:2:1:1:1 | 48 | несбалансированная |

| 12 | 2:1:2:1:2:1:2:1 | 64 | несбалансированная |

| 14 | 2:1:2:2:2:1:2:2 | 33 | несбалансированная |

| 16 | 2:2:2:2:2:2:2:2 | 100 | сбалансированная |

Максимизация полосы пропускания памяти

Чтобы максимизировать пропускную способность памяти сервера за счет технологии чередования, необходимо соблюдать следующие правила:

- ► Баланс памяти между процессорами — все сокеты процессора на одном физическом сервере должны иметь одинаковую конфигурацию модулей памяти DIMM

- ► Баланс памяти на контроллерах памяти — все контроллеры памяти в процессоре должны иметь одинаковую конфигурацию модулей памяти DIMM

- ► Баланс памяти по каналам памяти — все каналы памяти должны быть заполнены и иметь одинаковую общую емкость памяти и одинаковое общее количество ранков

Если серверу требуется заданная емкость памяти, может потребоваться меньшие по емкости модули DIMM или сочетание DIMM разных размеров для создания сбалансированной конфигурации памяти.

Например, может потребоваться 96 ГБ памяти на сервере с одним процессором Intel Xeon E5. Это может быть достигнуто с использованием шести модулей DIMM емкостью 16 ГБ. Но, к сожалению, нет способа следовать всем вышеизложенным правилам балансировки с шестью модулями DIMM на четырех каналах памяти. Вариантами в этой ситуации являются:

- ► Используйте двенадцать 8 ГБ модулей DIMM. Они будут расположены в виде конфигурации 3:3:3:3, которая будет соответствовать всем правилам балансировки.

- ► Используйте один 16 ГБ DIMM и один 8 ГБ DIMM на каждом канале.

- ► Установите больше памяти, чем требуется. Увеличение количества модулей требуется для создания сбалансированной конфигурации памяти. В этом случае восемь 16 ГБ модулей могут быть расположены как сбалансированная конфигурация памяти 2:2:2:2.

Важно создать сбалансированную конфигурацию памяти, следуя всем вышеприведенным правилам, чтобы максимизировать пропускную способность памяти и общую производительность сервера.

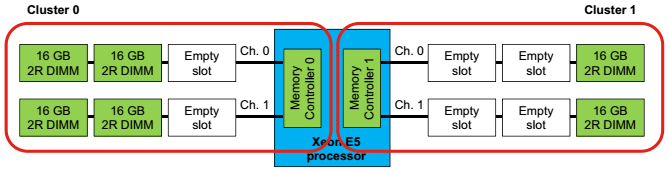

Влияние параметра Cluster on Die на пропускную способность памяти

Cluster on Die (CoD) — это параметр, устанавливаемый в UEFI BIOS и эффективно разбивающий процессор на две части, так что он действует как два процессора. Опция CoD доступна только на процессорах Intel Xeon E5-2600 v3 и Intel E5-2600 v4 с двумя контроллерами памяти — процессорами Intel Xeon E5 v3 с 10 или более ядрами и процессорами E5 v4 с 12 или более ядрами.

Конфигурации с включенной опцией CoD могут повысить производительность приложений, которые оптимизированы под Un-Uniform Memory Access (NUMA). Каждая половина процессора рассматривается как отдельный узел NUMA с исключительными правами на половину процессорных ядер, свой контроллер памяти и локально подключенную к нему память. Такая конфигурация может повысить производительность для приложений, данные которых находятся почти полностью внутри кластера, на котором он работает.

На рис. 21 на стр. 16 показан процессор Intel E5 с включенной опцией CoD, создающий два кластера.

(STREAM = 100)

Опция CoD может уменьшить влияние не выполняющегося правила балансировки памяти 2 на производительность системы. Больше памяти может быть подключено к одному контроллеру памяти, и при этом сохраняются условия для максимальной пропускной способности памяти. Это работает, если память сбалансирована по каналам памяти каждого из контроллеров памяти.

Без опции CoD в конфигурации 2:2:1:1 не поддерживается правило балансировки памяти 2, что делает ее несбалансированной конфигурацией и снижает пропускную способностью памяти. С опцией CoD конфигурация 2:2:1:1 обеспечивает максимальную пропускную способность памяти. Тем не менее, рекомендуется соблюдать все принципы сбалансированной памяти даже с конфигурациями с включенной опцией CoD.

Резюме

Общая производительность сервера зависит, в том числе, от производительности подсистемы памяти, которая может при правильной настройке обеспечить высокую пропускную способность и низкую задержку доступа к памяти. Балансировка памяти по контроллерам памяти и каналам памяти создает конфигурации, которые могут эффективно перемежать обращения к памяти между своими модулями DIMM, обеспечивая максимально возможную пропускную способность. Несбалансированная конфигурация может сократить общую пропускную способность до 16% от уровня, обеспечиваемого сбалансированной конфигурацией памяти.

Реализация всех трех правил балансировки памяти, описанных в этом документе, приводит к сбалансированным конфигурациям, обеспечивающим наилучшую пропускную способность подсистемы памяти и производительность системы в целом.

Авторы

Эта статья была подготовлена следующей командой специалистов:

Дэн Колглазиер (Dan Colglazier) является старшим инженером в группе Performance Data Center Data Center в Моррисвилле, Северная Каролина. Ранее он провел более 30 лет в IBM, где он начал работать в команде IBM Data Processing Division, помогая улучшить дизайн перспективных архитектур хранения мэйнфреймов. Основное внимание уделяется оценке производительности будущих серверов System x® как в IBM, так и в Lenovo. В настоящее время он является лидером команды по разработке дизайна. Дэн имеет степень бакалавра наук по вычислительной технике и степень магистра в области электротехники в обоих Университетах штата Иллинойс.

Джо Якубовски (Joe Jakubowski) — старший технический сотрудник в лаборатории Lenovo Server Performance Laboratory в Моррисвилле, Северная Каролина. Ранее он провел 30 лет в IBM. Он начал свою карьеру в тестовой организации подразделения IBM Networking Hardware Division и работал над различными адаптерами, коммутаторами и тестовыми инструментами Token Ring. Он провел последние 21 год в подразделении, занимающимся производительностью серверов, уделяя основное внимание работе с базами данных, виртуализацией и новыми технологиями. Его текущая роль включает в себя все аспекты архитектуры и производительности серверов x86. Джо имеет степень бакалавра наук в области электротехники и инженерных операций в Университете штата Северная Каролина и степень магистра в области телекоммуникаций из Университета Пейса.

Tristian «Truth» Brown — инженер по производительности оборудования в команде Lenovo Server Performance Team в Роли, штат Северная Каролина. Он отвечает за аппаратный анализ высокопроизводительных решений на основе флэш-памяти для серверов System x. Truth получил степень бакалавра по электротехнике в Университете штата Теннесси и степень магистра электротехники в Университете штата Северная Каролина. Его основные интересы были сконцентрированы в области разработки и проверки микропроцессора Computer Architecture и System-on-Chip (SoC).

Благодарность следующим людям за их вклад в этот проект:

Чарльз Стефан (Charles Stephan), команда разработчиков производительных серверов Lenovo

Дэвид Уоттс (David Watts), Lenovo Press

Перевод: SMB-Solution.